## CSCI 4974 / 6974 Hardware Reverse Engineering

Lecture 2: Packaging

## Packaging

- Bare silicon devices are useless if you can't talk to them

- Something has to connect them to the board

- To get to the silicon, we have to know what's in the way

#### Parts of an IC

- Die

The actual silicon "chip"

- Leadframe

Pins that are soldered to the board

- Molding compound

Protects die and wires

- Wires or bumps

Electrically connects die to leadframe

- Die attach

Mechanically connects die to leadframe

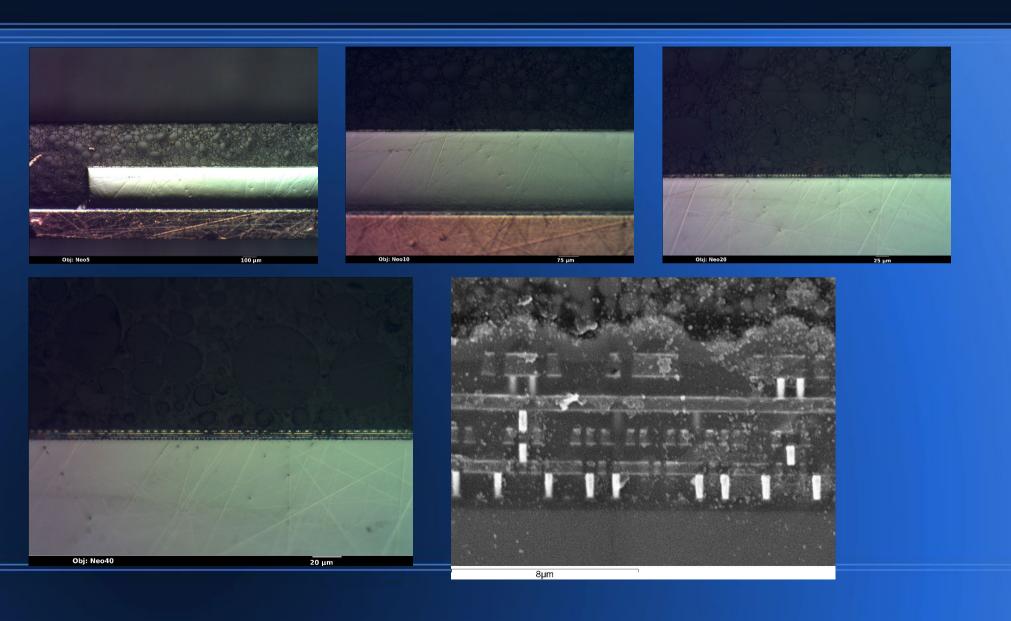

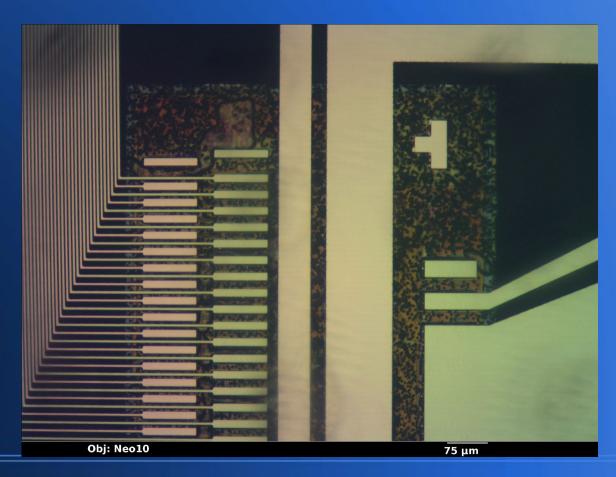

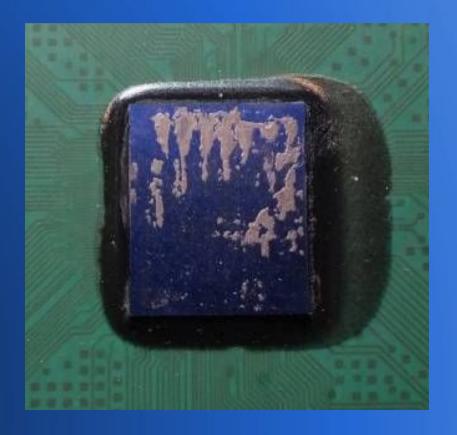

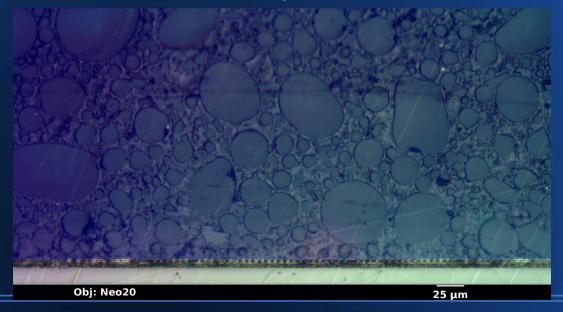

#### Die vs circuit thickness

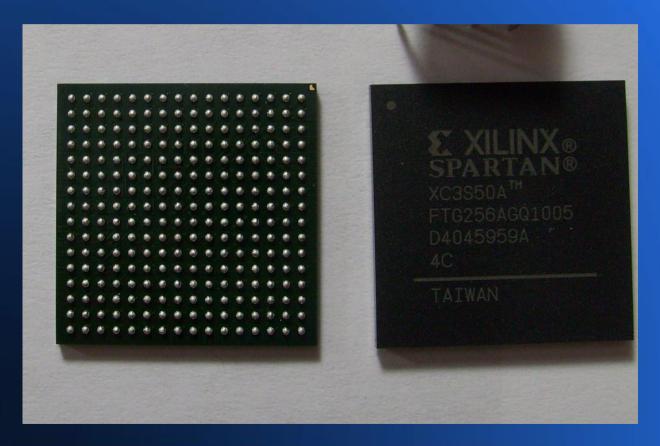

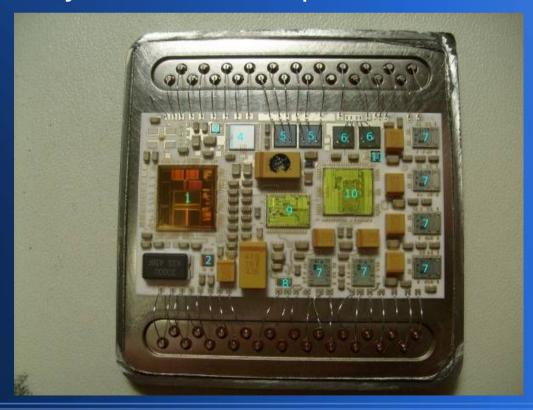

## Multi-die packages

- Several dies in one package

- FPGA + flash

- We may see one of these next Friday's lab

- MEMS + ASIC

- High-density NAND/DRAM

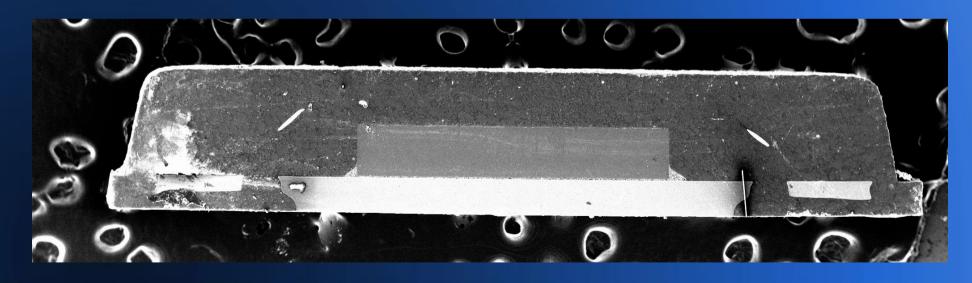

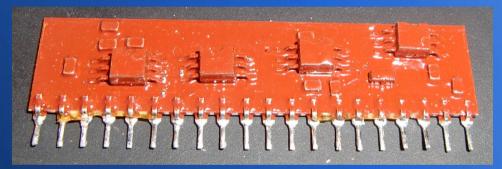

## Leadframe

The actual pins which get soldered to the board

## Package classification

- Material ceramic, plastic, etc

- Mounting type through hole or surface mount

- Cavity direction up/down

- Wire bond vs flip chip

- Through hole vs SMT

- Topology linear vs area array

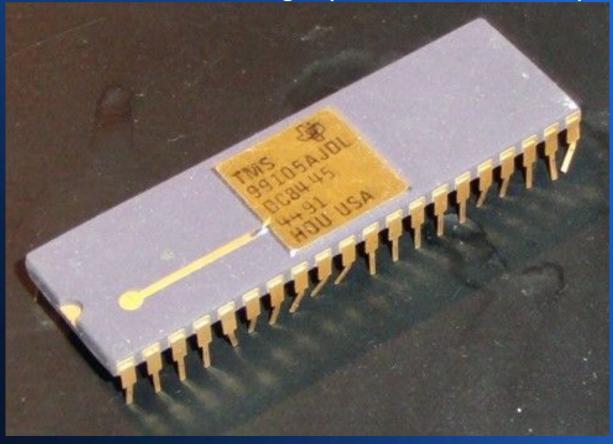

## Packaging evolution

- Large, fragile devices, low logic density

- Not many pins

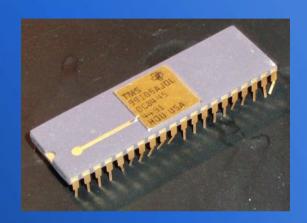

- Hermetically sealed packages required

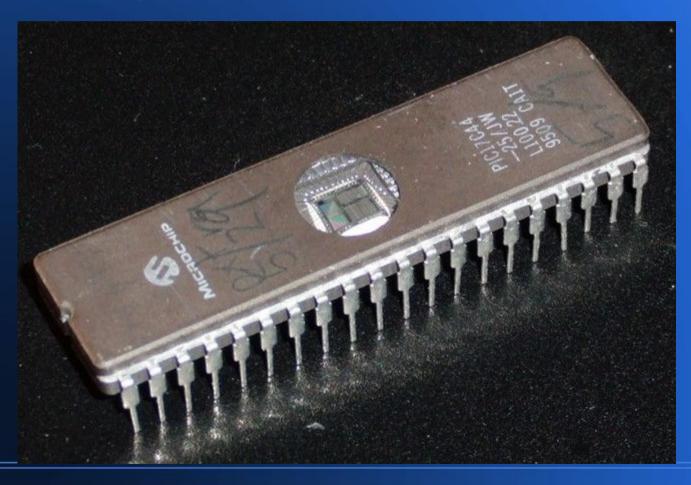

- EPROM needs UV exposure

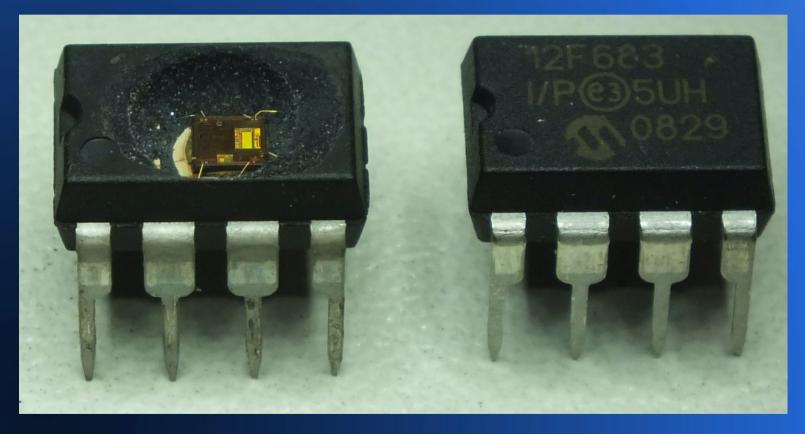

Ceramic Dual Inline Package (CDIP or CERDIP) w/ soldered lid

CDIP with window

## Packaging evolution

- Ceramic is expensive, can we do something cheaper?

- Plastic costs a lot less

- Ceramic is still used in rare cases (some mil-spec etc) but nearly unheard of in modern consumer devices

Plastic Dual Inline Package (PDIP)

## Packaging evolution

- DIPs waste a lot of space for high-density devices

- Drilling holes requires more manufacturing time

- Surface mount technology!

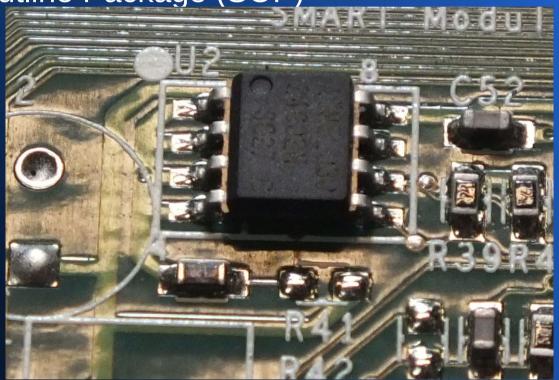

Small Outline IC (SOIC)

Small Outline Package (SOP)

## Packaging evolution

- Having pins on only two sides makes for long, skinny, awkwardly shaped packages

- What if we used all four?

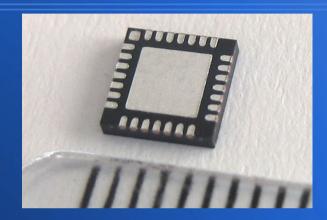

Quad Flat Pack (QFP)

Quad Flat No-Leads (QFN)

## Packaging evolution

- Even higher density is required for modern electronics

- Why only use the perimeter of the package?

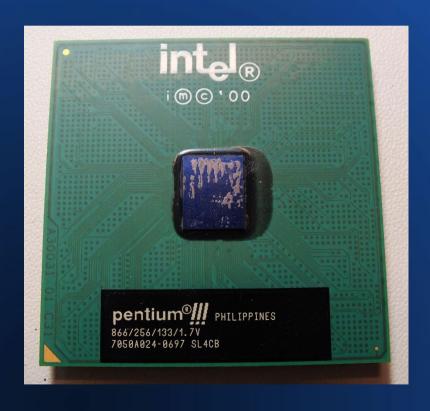

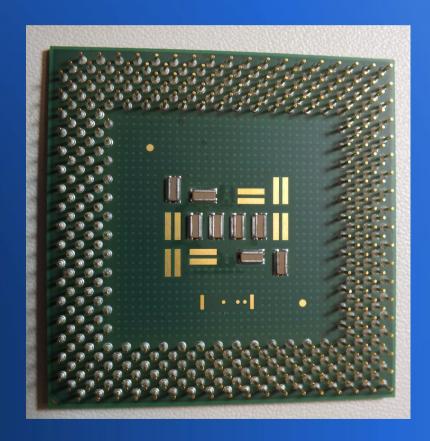

Pin-grid array (PGA)

Ball-grid array (BGA)

Column Grid Array (CGA)

Chip-scale BGA (CSBGA)

## Packaging evolution

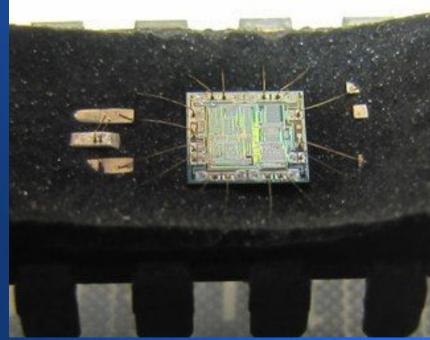

Special needs call for special device packages

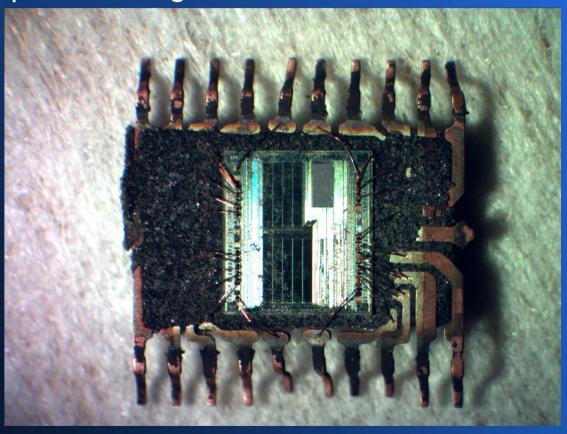

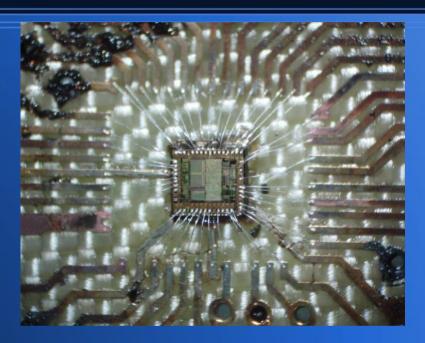

Chip on Board (COB)

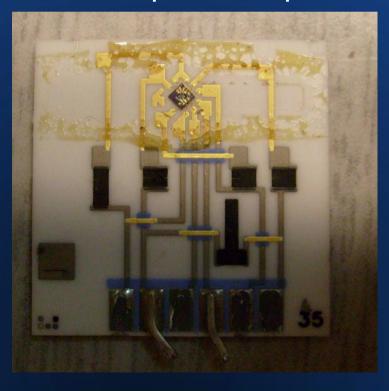

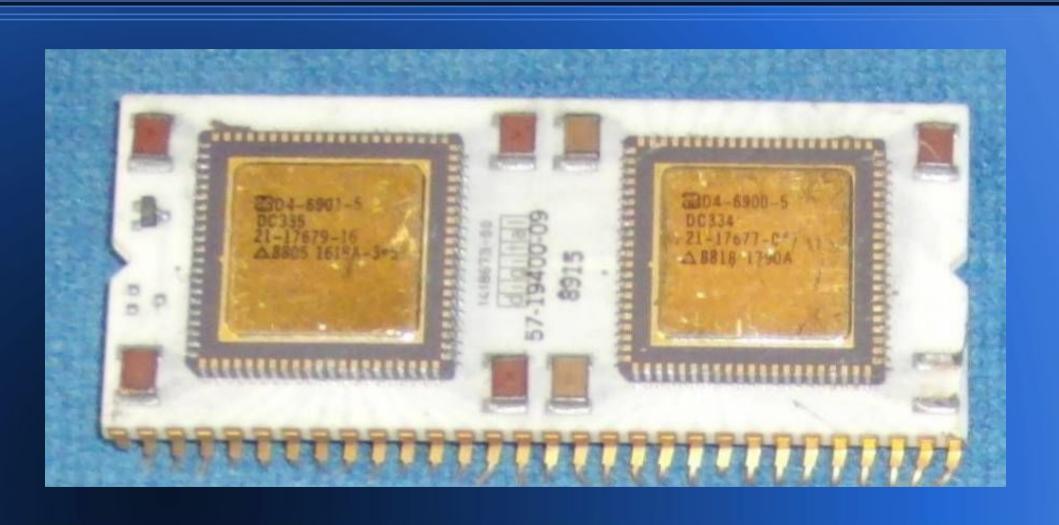

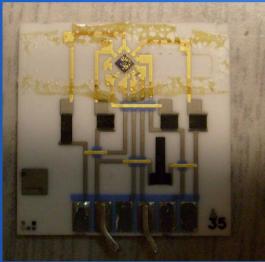

#### **Hybrid circuits**

- One or more dies bonded to a ceramic (usually) substrate

- Film passives printed directly on substrate, optional laser trim

## Chip on Glass (CoG)

- Die is attached directly to glass substrate

- Mostly used for LCDs

# Multichip module (MCM)

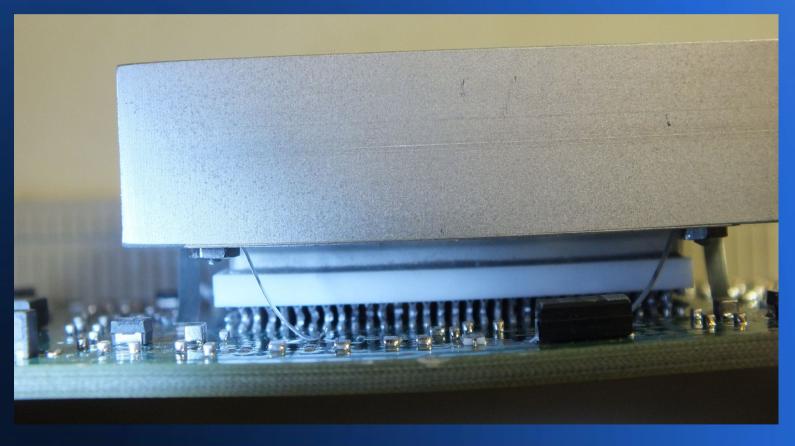

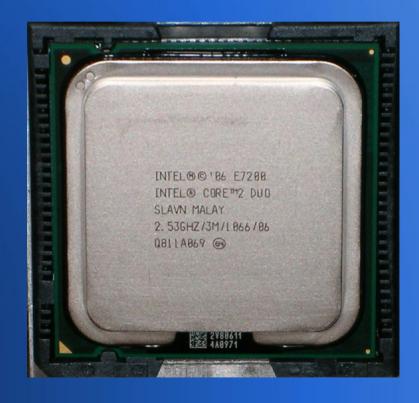

## Thermally enhanced packages

- Generally meant to be used with a heatsink

- Always flip-chip packaging

- Very difficult to microprobe

- Chip will fry if not cooled

- Extra care required to decap

#### **Double interposers**

- Die in a BGA package soldered to a larger BGA or PGA

- Very rare, I've only seen this once

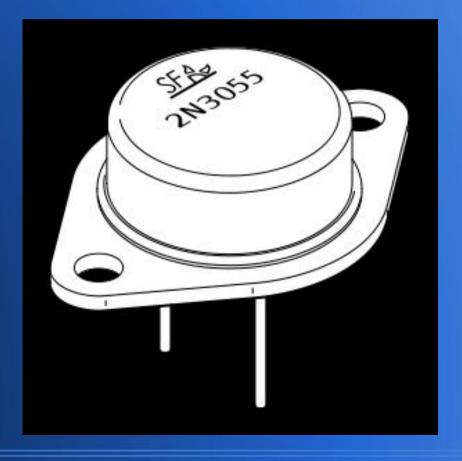

## Metal cans (TO-x)

- Often used for old discrete transistors, laser diodes

- Some military / automotive ICs

- Good thermal properties

- Glass/metal hermetic seal

- Low pin count

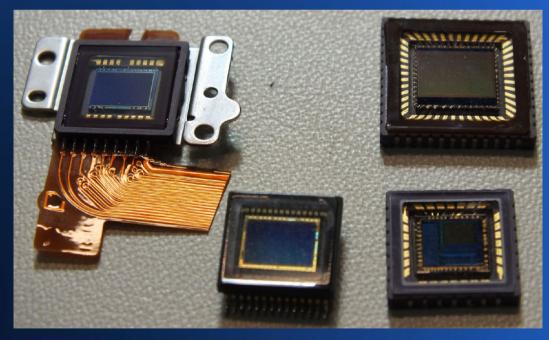

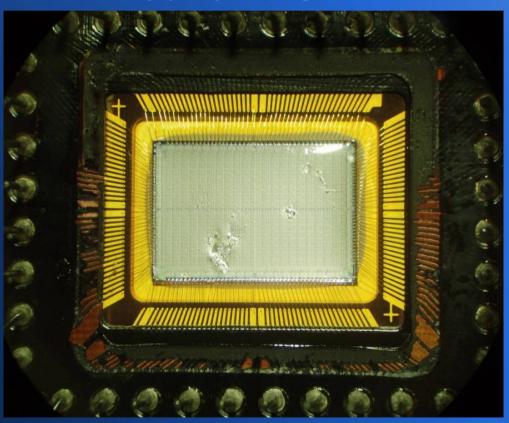

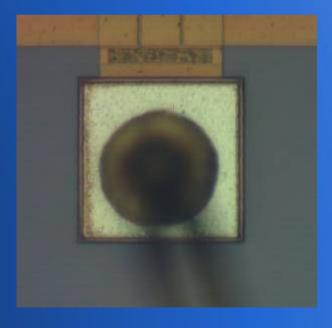

#### Camera sensors

- Package is optically transparent

- May not need to decap at all just image through window

- Typically ceramic with glass lid

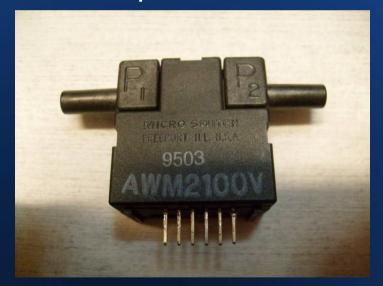

#### Other sensors

- Packaging varies widely depending on what's measured

- Example: MEMS mass airflow sensor

## **Potting**

- Protects board from water, dirt, etc

- May also make tampering harder

- Needs to be removed to get to chips or probe board

## Conformal coating

- Like potting, but a thin layer that doesn't fill the enclosure

- May be clear or opaque

#### **BGA** underfill

- Provides mechanical stability to balls

- Improves resistance to cracking

- Makes desoldering difficult

### Die coats

- Protection against particulates and (?) liquid ingress

- Polyimide film

- Silicone goo

# Package construction

How is the chip connected to the leadframe?

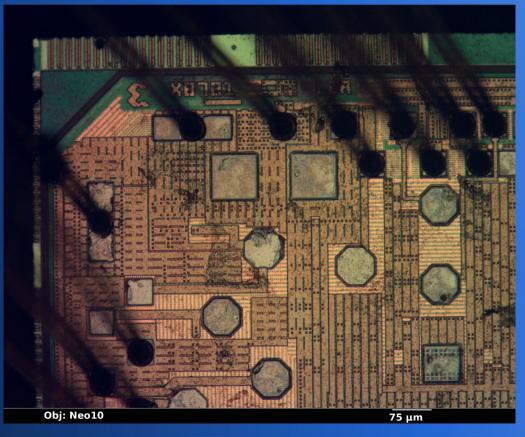

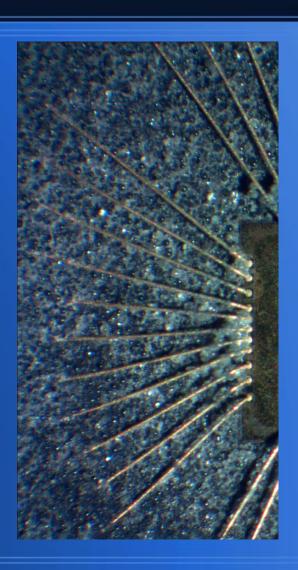

## Wire bonding

- Usually Au, but Al and Cu are used in special applications

- Cheapest way of connecting to leadframe

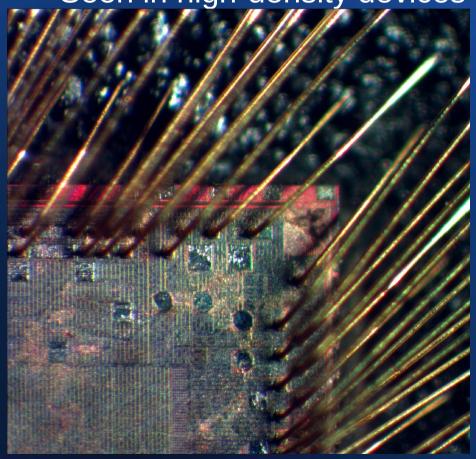

## **Concentric bond rings**

Seen in high-density devices

### **Double bonds**

- Two wires from die to the same package pin

- Indicates a high-current line (often power)

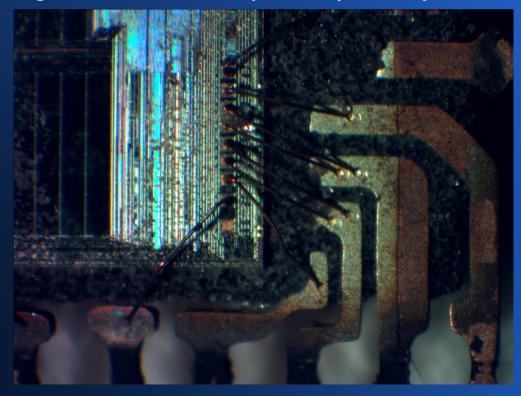

### **Ball bonding**

- Wire feeds through needle

- Electrically melt tip into a ball

- Press onto bond pad with needle

- Apply heat and ultrasound to weld

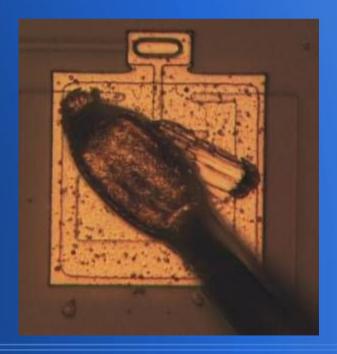

# Wedge bonding

- Wire feeds through wedge-shaped nozzle

- Press onto pad

- Apply heat and ultrasound to weld

- Note probe scrub from wafer test

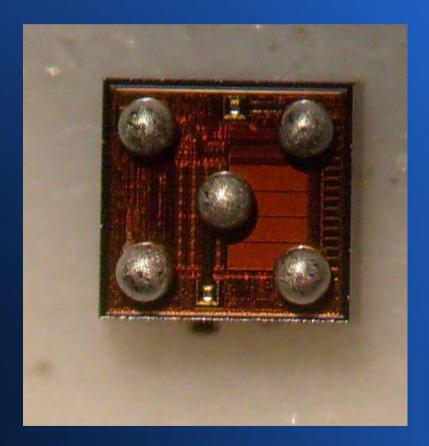

### Flip chip

- Large, high-performance devices with lots of pins

- Active side of die goes down

- Solder bumps from top metal layer to interposer

- Interposer is basically a fine-pitch PCB with lots of layers

- Breaks super-fine solder bumps out to saner pitch

- Front-side attacks very hard

- Back-side attacks easier, top of die is already exposed :D

## Carrier island / paddle

- Surface that the die rests on

- Typically connected to die substrate and electrically grounded

- Plastic packages: Cu with Sn plating

- Ceramic packages: Au plating over cofired leadframe metal

- Often fully covered by molding compound

- Exposed in QFNs for thermal reasons

#### Die attach

- Connects die to island

- Common materials:

- Silver epoxy

- Solder

- Au-Si eutectic alloy

- NanoFoil (Al-Ni + solder)

### Package materials

- To reverse the device, we have to get the package off

- Knowing exactly what it's made of helps

## Plastic package materials

- "Plastic" chips are not actually plastic!

- Normally a composite, glass beads in epoxy

- Wire bonds are Au / Cu

- Leadframes Sn, Cu

### Plastic package materials

- Epoxy is a thermoset (won't melt, just burns or decomposes)

- Glass content varies greatly, but is usually fairly high (>> 50%)

- Sometimes a lot higher!

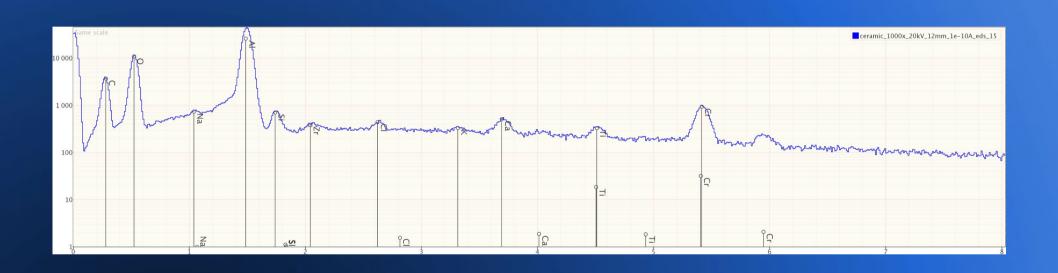

### Ceramic package materials

- Fired ceramic clays

- Pieces often held together with glass

- Cofired packages use Mo or W interconnect

- Lids may be held on with solder or glass

- Extremely chemical resistant, very little will etch it

- Very good seals, used for high-reliability applications

- Brittle, can crack

### Ceramic package materials

- Can be white, brown, or purple

- Al<sub>2</sub>O<sub>3</sub> is by far the most common ceramic

- Often mixed with SiO<sub>2</sub>

- AlN and BeO are used in some special cases, rare

- All are colorless

- Brown color comes from a few percent of MnO

# Purple ceramic analysis

### Questions?

- TA: Andrew Zonenberg <azonenberg@drawersteak.com>

- Image credit: Some package images are CC-BY from:

- John McMaster < John DMcMaster@gmail.com>

- marshallh